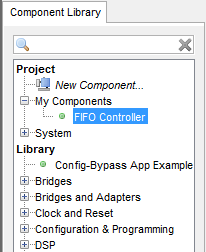

FPGA SPI Bridge Console for Avalon Bus(3)FIFO Controllerコンポーネントを作成

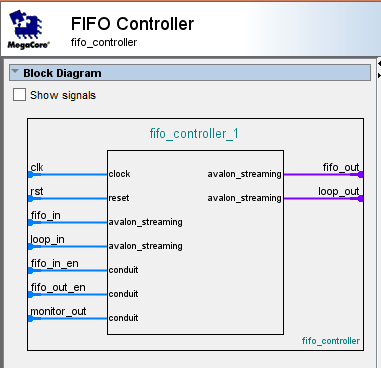

前回追加した入出力共Avalon-STのFIFOにAndroid端末からAvalon-MM経由でデータを書き込み、その後FIFOの出力を入力に繋いでDACからループ出力させます。そのための独自のQsysコンポーネントFIFO Controllerを作ります。

Verilogの記述は次のようにシンプルです。

// fifo_controller.v // This file was auto-generated as a prototype implementation of a module // created in component editor. It ties off all outputs to ground and // ignores all inputs. It needs to be edited to make it do something // useful. // // This file will not be automatically regenerated. You should check it in // to your version control system if you want to keep it. `timescale 1 ps / 1 ps module fifo_controller #( parameter AUTO_CLK_CLOCK_RATE = "-1" ) ( input wire clk, // clk.clk input wire rst, // rst.reset input wire [31:0] fifo_in_data, // fifo_in.data input wire fifo_in_valid, // .valid output wire fifo_in_ready, // .ready output wire [31:0] fifo_out_data, // fifo_out.data output wire fifo_out_valid, // .valid input wire fifo_out_ready, // .ready input wire [31:0] loop_in_data, // loop_in.data input wire loop_in_valid, // .valid output wire loop_in_ready, // .ready output wire [31:0] loop_out_data, // loop_out.data output wire loop_out_valid, // .valid input wire loop_out_ready, // .ready input wire fifo_in_en, // fifo_in_en.export input wire fifo_out_en, // fifo_out_en.export output wire [31:0] monitor_out // monitor_out.export ); assign loop_in_ready = fifo_out_en == 1'b1 ? fifo_out_ready : 1'b1; assign fifo_out_valid = loop_in_valid; assign fifo_out_data = loop_in_data; assign fifo_in_ready = fifo_in_en == 1'b1 ? loop_out_ready : 1'b0; assign loop_out_valid = fifo_in_en == 1'b1 ? fifo_in_valid : loop_in_valid; assign loop_out_data = fifo_in_en == 1'b1 ? fifo_in_data : loop_in_data; assign monitor_out = loop_out_data; endmodule

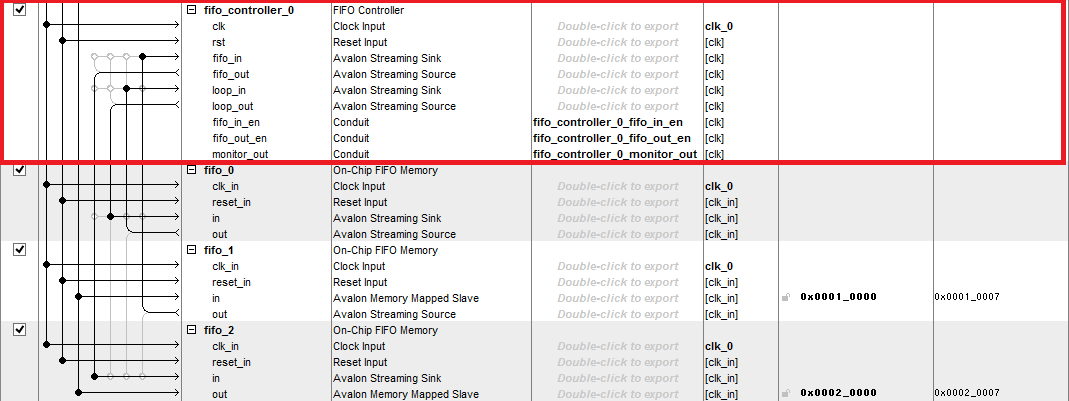

Qsys上でFIFOと繋ぎます。

Top-levelのVerilogはこうなりました。

module ledtest (

RST_N,

CLK,

SPI_NSS,

SPI_SCLK,

SPI_MISO,

SPI_MOSI,

LED2,

LED4,

LED5,

DAC

);

input CLK, RST_N;

input SPI_NSS, SPI_SCLK, SPI_MOSI;

output SPI_MISO;

output LED2, LED4, LED5;

output [11:0] DAC;

wire [2:0] leds_sig;

wire [31:0] monitor_out;

spi_master u0 (

.clk_clk (CLK),

.reset_reset_n (RST_N),

.spi_slave_to_avalon_mm_master_bridge_0_export_0_mosi_to_the_spislave_inst_for_spichain (SPI_MOSI),

.spi_slave_to_avalon_mm_master_bridge_0_export_0_nss_to_the_spislave_inst_for_spichain (SPI_NSS),

.spi_slave_to_avalon_mm_master_bridge_0_export_0_miso_to_and_from_the_spislave_inst_for_spichain (SPI_MISO),

.spi_slave_to_avalon_mm_master_bridge_0_export_0_sclk_to_the_spislave_inst_for_spichain (SPI_SCLK),

.pio_0_external_connection_export (leds_sig),

.fifo_controller_0_monitor_out_export (monitor_out),

.fifo_controller_0_fifo_in_en_export (leds_sig[0]),

.fifo_controller_0_fifo_out_en_export (leds_sig[1])

);

assign LED2 = ! leds_sig[0];

assign LED4 = ! leds_sig[1];

assign LED5 = ! leds_sig[2];

assign DAC = {monitor_out[9:0], 2'b00};

endmodule

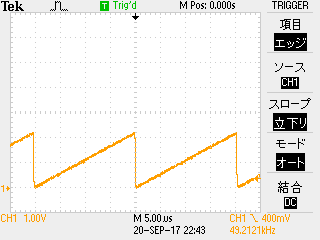

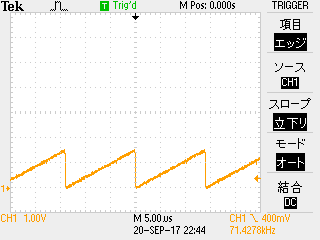

1024ワードのFIFOに1024ワードのインクリメンタルパターンを書いた場合と、700ワードを書いた場合の出力波形です。FIFOに書いた分でループします。